全相联cache设计及logisIM连接图

”cache 全相联 直接相联 组相联“ 的搜索结果

详细介绍了cache缓存与主存之间的三种映射方式及其区别

全相联cache设计 存储系统设计(HUST) 计算机组成原理

logisim全相联cache设计.txt

头歌计算机组成原理2路组相联cache设计头歌计算机组成原理2路组相联cache设计头歌计算机组成原理2路组相联cache设计头歌计算机组成原理2路组相联cache设计头歌计算机组成原理2路组相联cache设计头歌计算机组成原理2...

1、实验目的 3 2、实验内容 3 3、实验原理 3 4、实验准备 5 5、实验步骤 8 1、实验目的 2、实验内容 3、实验原理 4、实验准备 5、实验步骤

计算机组成原理有关直接相联映射Cache的实验报告

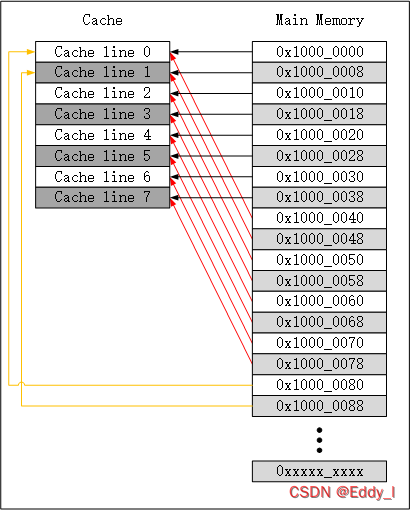

Cache的地址映射中,会以Cache的容量为标准将内存分成相同大小的块(页或者区),根据映射方法的不同,地址的表达方式也不同,常见的映射方式分为:直接映射、全相联映射和组相联映射。

第5关:直接相联cache设计.txt

为了解决之间的矛盾,把各种不同存储容量,不同存取速度,不同价格的存储器,按照一定的体系结构组织起来,使所存放的程序和数据按层次分布在各存储器中,形成---常见的就是三级存储系统,即:Cache、主存、辅存。...

模拟cache直接映射。实现原数据与cache现有数据的比较及更新,实现多行的输出。采用logisim软件设计仿真和调试完成。 1.2 总体设计 1.2.1 总体设计原理 cache的原理机制。由于主存的取存速度较慢,通过cache高速的取...

(深圳)实验作业 开课学期: 2021春季 课程名称: 计算机组成原理(实验) 实验名称: 直接相联Cache设计 实验性质: 综合设计型 实验学时: 4 地点

华中科技大学-Cache直接相联映射

标签: 学习

计算机系统结构课程使用logsim实现的cache,得到A、92分,注意logsim版本为logisim-evolution-google

---- Cache的容量很小,它保存的内容只是主存内容的一个子集,且Cache与主存的数据交换是以块(cache line)为单位的。为了把信息放到Cache中,必须应用某种函数把主存地址...Cache的地址映射方式有直接映射、全相...

直接映射优缺点 - 优点: 硬件实现简单,成本低. - 缺点: 灵活性差。每个主存块只有一个固定的行可以存放,因此即便cache中有大量空闲...- 优点: 全相联映射方式比较灵活,主存的地址可以映射到Cache的任一cache line

头歌计算机组成原理全相联cache设计头歌计算机组成原理全相联cache设计头歌计算机组成原理全相联cache设计头歌计算机组成原理全相联cache设计头歌计算机组成原理全相联cache设计头歌计算机组成原理全相联cache设计头...

Cache与主存之间的全相联映射,直接映射和组相联映射的区别 1.高速缓冲存储器的功能、结构与工作原理 高速缓冲存储器是存在于主存与CPU之间的一级存储器,由静态存储芯片(SRAM)组成,容量比较小但速度比主存高得...

全相联cache设计

标签: c++

全相联cache设计

以下用图书馆坐座位的例子来说一说直接映射、全相联映射和组相联映射。 对于直接映射,每个块在cache中只能有一个位置,非常局限,就好像图书馆里有那么多空位,你却只能坐在一个地方,即使别的地方是空的你也不能坐...

Cache高速缓存 基本描述 位于CPU和主存之间;容量一般在几千字节到几兆字节之间;速度比主存快5-10倍; 由快速半导体组成、按内容存取 Cache访问速度仅此于CPU 局部性原理 Cache改善系统性能的依据是局部性原理...

Cache组相联映射相关计算

标签: 经验分享

某计算机的Cache共有16块,采用2路组相联映射方式(即每组2块)。每个主存块大小为32字节,按字节编址。主存129 号单元所在主存块应装入到的Cache组号是?最后我们计算应该装入到cache中的组号 i = k mod n = 4 mod 8 ...

推荐文章

- Unity3D 导入资源_unity怎么导入压缩包-程序员宅基地

- jqgrid 服务器端验证,javascript – jqgrid服务器端错误消息/验证处理-程序员宅基地

- 白山头讲PV: 用calibre进行layout之间的比对-程序员宅基地

- java exit方法_Java:如何测试调用System.exit()的方法?-程序员宅基地

- 如何在金山云上部署高可用Oracle数据库服务_rman target sys/holyp#ssw0rd2024@gdcamspri auxilia-程序员宅基地

- Spring整合Activemq-程序员宅基地

- 语义分割入门的总结-程序员宅基地

- SpringBoot实践(三十五):JVM信息分析_怎样查看springboot项目的jvm状态-程序员宅基地

- 基于springboot+vue的戒毒所人员管理系统 毕业设计-附源码251514_戒毒所管理系统-程序员宅基地

- 【LeetCode】面试题57 - II. 和为s的连续正数序列_leet code 和为s的正数序列 java-程序员宅基地